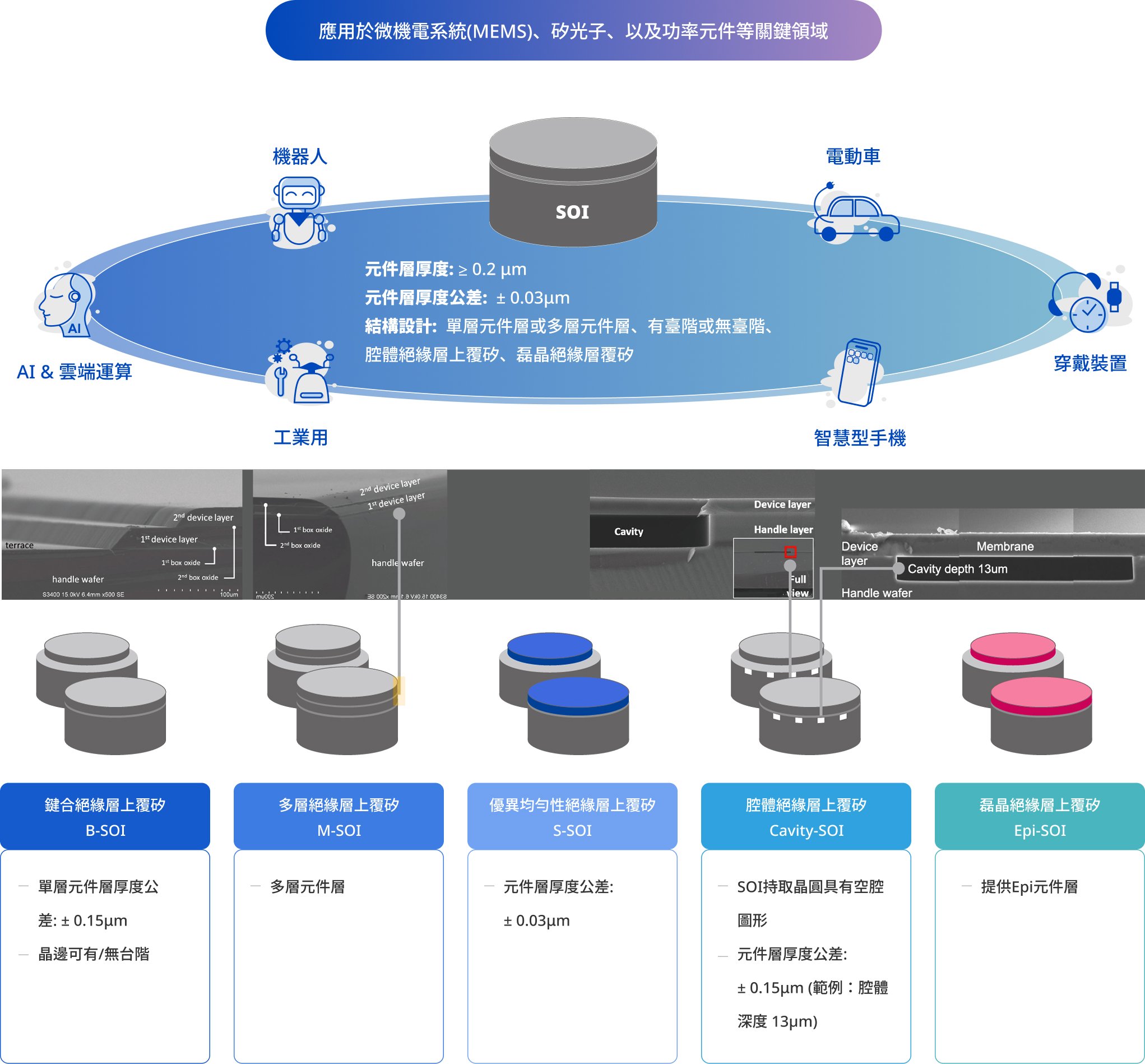

M-SOI(Multi-layers SOI)

多層器件層 SOI 晶圓

M-SOI不只是單層的矽/氧化層結構,而是透過精密製程在同一晶圓上實現多層矽器件層 (Device Layers) 的垂直堆疊,每層之間由絕緣埋氧層 (BOX) 完美隔離。

產品技術優勢

1.極致隔離,消除干擾

- 優化描述:利用多層 BOX 物理隔絕,將寄生電容與電串擾降至最低。

- 應用價值:對於 AI 資料中心所需的高速光路傳輸而言,這是確保訊號純淨,降低誤碼率的最佳選擇。

2.高集成度:縮小使用面積

- 優化描述:實現垂直3D整合,將感測器、驅動電路與處理器疊在一起。

- 應用價值:對接CPO (共同封裝)需求,解決機櫃空間受限問題。

3.設計自由度:異質整合的起點

- 優化描述:每層矽層的厚度、摻雜濃度、晶體取向均可獨立客製化。

- 應用價值:第一層用來做低功耗運算,第二層用來承受高電壓驅動 MEMS。

典型規格範圍(可客製)

|

項目 |

規格範圍 |

|---|---|

|

晶圓尺寸 |

6 吋 / 8 吋(依專案評估) |

|

Device Layer 厚度 |

± 0.45µm – 305µm |

|

BOX 厚度 |

± 0.1 – 5µm |

|

電阻率 |

依客戶需求指定 |

|

表面粗糙度 |

符合高階 MEMS 要求 |

主要應用

MEMS 元件

- 壓力感測器

- 加速度計 / 陀螺儀

- 微鏡(MEMS Mirror)

Please reach us at : [email protected]