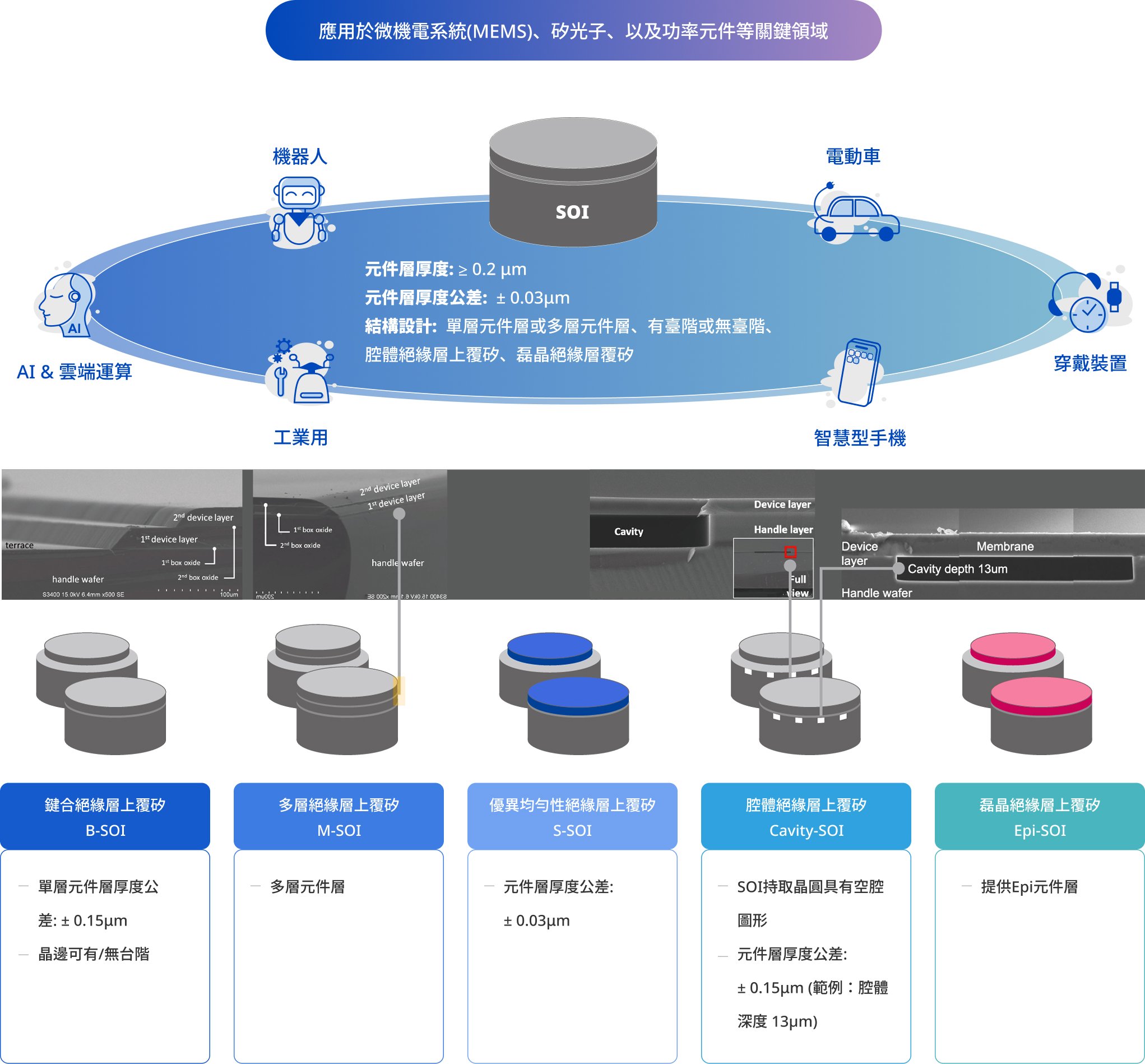

S-SOI (Superior-SOI)

在SOI晶圓的製造流程中,器件層(Device Layer)厚度的均勻性,是決定終端半導體元件性能,可靠度與量產良率的核心指標。

隨著新高精度 MEMS 感測器與矽光子(Silicon Photonics)元件,對厚度公差的要求快速收斂至奈米甚至次奈米尺度,傳統減薄與化學機械拋光(CMP)技術,正逐步逼近其物理與製程極限。

在此背景下,離子束加工減薄(Ion Beam Trimming, IBT)作為一種超精密表面修整技術,已成為確保 S-SOI 基板達成極致厚度均勻性 的關鍵製程。

典型規格範圍(可客製)

|

項目 |

規格範圍 |

|---|---|

|

晶圓尺寸 |

6 吋 / 8 吋(依專案評估) |

|

Device Layer 厚度 |

± 0.45µm – 305µm |

|

BOX 厚度 |

± 0.1 – 5µm |

|

電阻率 |

依客戶需求指定 |

|

表面粗糙度 |

符合高階 MEMS 要求 |

主要應用

- 高精度 MEMS 與感測器

- 矽光子(Silicon Photonics)

- 低功耗、高效能運算與 IoT 元件

Please reach us at : [email protected]